Analog Basics—Part 2: Delta-Sigma (ΔƩ) ADCs and How to Exploit Their Digital Capabilities

Contributed By DigiKey's North American Editors

2020-05-14

Editor’s Note: Analog-to-digital converters (ADCs) connect the analog to the digital world and so are a fundamental component of any electronic system that connects to the real world. They are also a key determining factor of a system’s performance. This series explores the fundamentals of ADCs, their various types, and their application. Part 1 of this series on analog basics discussed SAR ADCs. Here, Part 2 discusses delta-sigma (ΔƩ) converters. Part 3 looks at pipeline ADCs. Part 4 shows how delta-sigma ADCs can generate ultra-low noise results. Part 5 explores difficult input driving issues for SAR ADCs.

As seen with the successive approximation register (SAR) analog-to-digital converter (ADC) discussed in Part 1, the high-precision challenge of an analog sensor signal chain—with multiple gain, signal conditioning, and complex analog filtering stages, all feeding into a SAR-ADC—can lead to analog missteps. Designers can also end up with an expensive, densely populated pc board solution.

Additionally, starting with the ultra-low sensor signals, the output of each analog stage in the signal chain contributes errors that manifest at the converter’s digital output as a low signal-to-noise ratio (SNR) and high distortion errors. Designers of such systems need to step back and rethink the high-precision sensor ADC paradigm.

The solution to the problems associated with a high-precision sensor system is to select an ADC topology that quickly digitizes the small sensor signal and digitally implements the noisy analog functions of gain and filtering. This is the role of the delta-sigma (ΔƩ) ADC.

This article briefly describes the fundamental function of a ΔƩ ADC and the internal analog-to-digital conversion mechanics using Analog Devices’ AD4110-1 universal input analog-to-digital front-end as an example. From there, it delves into a view of the surrounding signal chain and provides critical specs for a suitable data acquisition system.

The structure of a ΔƩ ADC

Just before the turn of the century, the ΔƩ ADC stole the analog spotlight. With the widespread adoption of ΔƩ’s advanced technology, the primary analog signal and computation processes began to reside in the digital domain. An examination of the ΔƩ ADC integrated circuit (IC), shows that over 80% of the silicon real estate executes digital functions. The by-product of the predominately digital circuitry is robustness and a small footprint.

How was this possible? It starts with the direct digitization of low-voltage analog signals. Once in the digital domain, digital circuitry can almost entirely replace analog filtering while also performing any required gain functions (Figure 1). Digital circuitry also shrinks with each semiconductor process node.

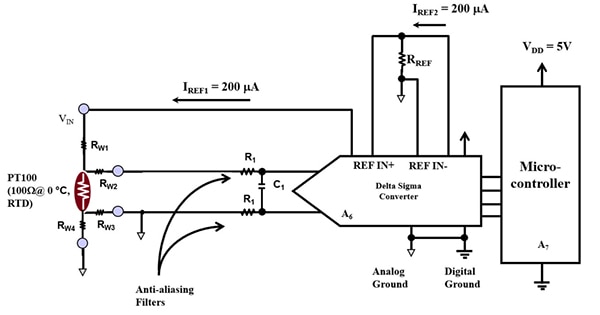

Figure 1: A ΔƩ contains almost all the necessary circuitry for filtering and gain. In this example, a ΔƩ ADC senses and digitizes the small resistance temperature detector (RTD) voltage. It then uses internal digital signal gain and filtering to render a low-noise 24-bit digital result. (Image source: A Baker’s Dozen)

Figure 1: A ΔƩ contains almost all the necessary circuitry for filtering and gain. In this example, a ΔƩ ADC senses and digitizes the small resistance temperature detector (RTD) voltage. It then uses internal digital signal gain and filtering to render a low-noise 24-bit digital result. (Image source: A Baker’s Dozen)

In Figure 1, the 24-bit ΔƩ ADC system consists of an analog input, a central digital engine, and a digital I/O terminal. The converter acquires the low-voltage RTD signal, and through digital filtering, produces a full 24-bit digital representation of the analog input. An analog gain block—usually dominant in SAR-ADC circuits—does not exist here, and the only analog filter is the combination of R1 and C1. Yes, this is a simple, inexpensive first-order filter!

How the ΔƩ ADC works

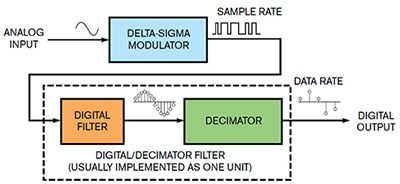

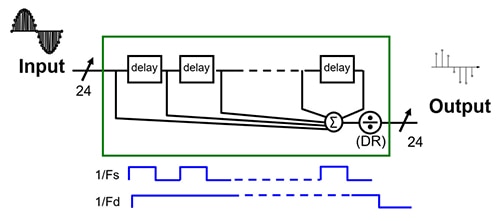

The basic topology of a ΔƩ ADC has a ΔƩ modulator in series with a digital filter. Beyond this basic topology, most ΔƩ ADCs have a variety of other features. However, all ΔƩ converters possess this essential core (Figure 2).

Figure 2: Stripped down to its basics, every ΔƩ ADC has a ΔƩ modulator, digital filter, and decimator. (Image source: EDN)

Figure 2: Stripped down to its basics, every ΔƩ ADC has a ΔƩ modulator, digital filter, and decimator. (Image source: EDN)

In Figure 2, the input can be sinusoidal or DC; this discussion will focus on a sinusoidal input. The ΔƩ modulator digitizes a single cycle sine wave to a 1-bit stream. The ΔƩ modulator output sample frequency is Fs. Although the 1-bit modulator conversion appears to have a high quantization noise, the signal noise is actually “shaped” into the higher frequencies. This paves the way for a low-noise, high-resolution conversion at the output of the digital filter.

At the output of the modulator, the digital filter accumulates the ΔƩ modulator’s 1-bit results and performs filter calculations. The digital filter output signal digitally reflects the analog input signal while continuing with an output frequency Fs. The signal now exclusively resides in the digital domain. A digital low-pass filter, or decimation filter, attenuates higher frequency noise and slows down the output data rate, 1/Fd. The digital/decimator filter samples and filters the modulator 1-bit code stream to a slower multi-bit code.

While most converters have only one sample rate, the ΔƩ converter has two: the input sampling frequency (Fs) and the output data frequency (Fd). The ratio of these two frequency variables defines the system decimation ratio (DR), per Equation 1:

![]() Equation 1

Equation 1

ΔƩ modulator

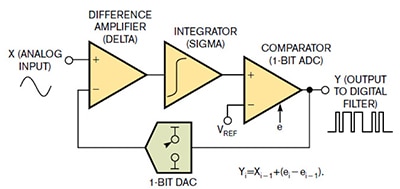

The ΔƩ modulator performs the actual analog-to-digital conversion by producing a stream of 1-bit codes. This process starts at a difference amplifier (Figure 3).

Figure 3: The ΔƩ ADC modulator input stage senses the delta between the analog input and the feedback DAC. The second stage implements an integrator function or sigma on the analog signal. (Image source: EDN)

Figure 3: The ΔƩ ADC modulator input stage senses the delta between the analog input and the feedback DAC. The second stage implements an integrator function or sigma on the analog signal. (Image source: EDN)

In Figure 3, the difference amplifier (delta) transmits the analog signal to an integrator (sigma). At the output of the integrator, a comparator differentiates at a very high sample rate (1/Fs) between the integrator’s output and a voltage reference (VREF). Additionally, the comparator presents the 1-bit stream to the 1-bit digital-to-analog converter (DAC). The modulator then measures the difference between the analog input signal and the analog output of the feedback DAC.

The ΔƩ >modulator shapes the noise out to higher frequencies through the action of the integrator and the DAC feedback loop. The formula in Figure 3 (bottom right) shows the transfer equation as Yi = Xi-1 + (ei – ei-1). The modulator digitizes the input signal (Xi) to a 1-bit output code (Yi) with a quantization noise (ei). Specifically, the output of the modulator (Yi) equals the input (Xi-1) plus the quantization noise (ei – ei-1). The formula shows the quantization noise as a difference between the current error (ei) minus the modulator’s previous error (ei-1).

Digital and decimation filters

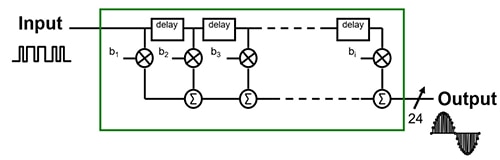

Averaging is a form of digital filtering, common in low-speed industrial ΔƩ ADCs. Almost all industrial ΔƩ ADCs incorporate the class of averaging filters called sinc filters that use a linear-phase finite-impulse-response (FIR), which is a digital low-pass filter (Figure 4).

Figure 4: The coefficients (bx) in this averaging FIR digital filter all equal one. (Image source: DigiKey)

Figure 4: The coefficients (bx) in this averaging FIR digital filter all equal one. (Image source: DigiKey)

In Figure 4, the modulator output bitstream is the input to this digital filter, and the modulator’s sampling clock determines the delay timing. Figure 4’s coefficients (bx) for FIR filters all equal one. With this averaging algorithm, the FIR digital filter generates a low-noise, 24-bit digital representation of the analog input in Figure 3, with samples occurring at the modulator’s sample rate (1/Fs). The decimation filter then reduces the output data rate, using the DR.

In the literature, the term “decimation” relates to the military act of systematically removing unwanted soldiers. Decimation in digital electronics uses the same concept to reduce the digital signal’s output data rate (1/Fd) by the DR. The expeditious and digital way to do this is to systematically discard some of the digital filter’s output samples (Figure 5).

Figure 5: The decimation process systematically reduces the number of digital 24-bit outputs by a factor of the output data rate (1/Fd, at bottom of image) divided by the sample rate (1/Fs). (Image source: DigiKey)

Figure 5: The decimation process systematically reduces the number of digital 24-bit outputs by a factor of the output data rate (1/Fd, at bottom of image) divided by the sample rate (1/Fs). (Image source: DigiKey)

The decimation process in Figure 5 decimates the output data rate (1/Fd) by the DR, per Equation 1.

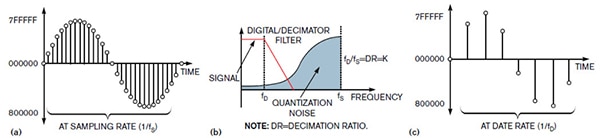

The events through the digital and decimation filter effectively reduce the ΔƩ ADC noise (Figure 6).

Figure 6: Shown here, the digital filter output (a) in the time domain; the modulator noise-shaped output superimposed on the decimation filter low-pass function (b); and the decimator’s output signal in the time domain (c). (Image source: EDN)

Figure 6: Shown here, the digital filter output (a) in the time domain; the modulator noise-shaped output superimposed on the decimation filter low-pass function (b); and the decimator’s output signal in the time domain (c). (Image source: EDN)

Figure 6 shows the digital signal as it travels through the digital/decimation filter. The digital filter 24-bit output (Figure 6(a)) runs at the same rate as the modulator sampling rate (1/Fs). The modulator has already shaped the quantization noise into higher frequencies (Figure 6(b)), so the digital/decimation filter captures the lower frequency portion of the output signal. The decimation filter (Figure 6(c)) output produces a lower frequency digital representation of the original analog signal.

Digital expansion

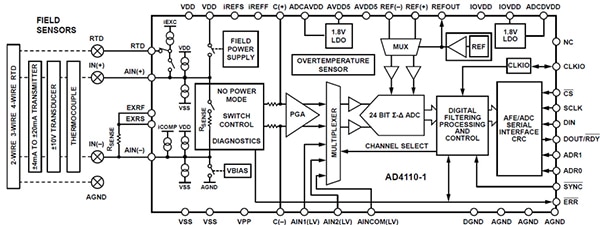

The ΔƩ ADC primarily resides in the digital domain. Now, digitally programmable gain stages, currents sources, short or open circuit input signal indicators, and various serial output interfaces can be easily added (Figure 7).

Figure 7: The AD4110-1 from Analog Devices provides multiple analog front-end functions for industrial process control systems. (Image source: Analog Devices)

Figure 7: The AD4110-1 from Analog Devices provides multiple analog front-end functions for industrial process control systems. (Image source: Analog Devices)

Figure 7 shows that the AD4110-1 ΔƩ ADC from Analog Devices has numerous digital enhancements including programmable input terminals, diagnostic functions, and flexible data rates. The input ready sensor interfaces include RTD and thermocouple temperature sensors.

The AD4110-1 has the basic core of a ΔƩ ADC, but the device’s digital emphasis enables an array of digitally enabled functions to the extent that the AD4110-1 is now a universal analog front-end (AFE).

As with a standard ΔƩ ADC, the AD4110-1 is capable of digitizing extremely low voltages from thermocouples, RTDs, and bridges. While these functions often require additional excitation circuitry, the AD4110-1 has them integrated on board.

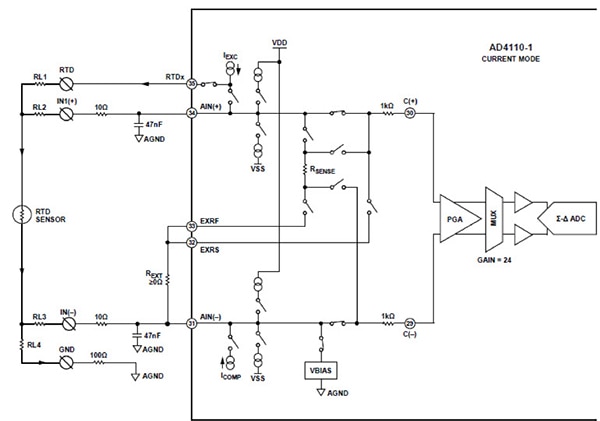

For instance, the RTD requires a precision current source that is ratiometric to the converter’s voltage reference (Figure 8).

Figure 8: Appropriate wire connections for a four-wire RTD and the AD4110-1 ΔƩ ADC. The RTD excitation current is programable at six levels between 0.1 milliamps (mA) and 1 mA. (Image source: Analog Devices)

Figure 8: Appropriate wire connections for a four-wire RTD and the AD4110-1 ΔƩ ADC. The RTD excitation current is programable at six levels between 0.1 milliamps (mA) and 1 mA. (Image source: Analog Devices)

In Figure 8, the AD4110-1 includes an excitation current that can be programmed to six levels between 0.1 mA and 1 mA using the converter’s PGA_RTD_CTRL register. The excitation current to the RTD resistor is from pin 35. The converter senses the voltage drop across the RTD via pins 34 and 31 high impedance inputs. The AD4110-1 programmable gain amplifier (PGA) offers 16 programmable gains of 0.2 to 24 volts/volt. With this feature, the designer is able to further complement the input sensor to the AD4110-1 input range. Other auxiliary capabilities include pull-up/pull-down currents to sense the presence of an open wire (useful with thermocouples), gain calibration, and correction coefficients.

Conclusion

The ΔƩ ADC eliminates complex analog front-end circuitry and provides a high-resolution, digitally averaged low-noise digital output signal by using a front-end modulator, an FIR digital filter, and a decimation filter. As much of the circuitry is in digital form, it can scale easily with advanced digital process nodes, and more functionality can be added while maintaining a small footprint and reduced board complexity.

The AD4110-1 ΔƩ ADC from Analog Devices takes advantage of the characteristics of this ADC architecture. The AD4110-1 has the basic core of a ΔƩ ADC, but the device’s digital emphasis enables an array of digitally enabled functions to the extent that the AD4110-1 is now a universal AFE and truly RTD and thermocouple ready.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.