Analog Basics—Part 4: Optimizing Delta-Sigma ADCs for Low Noise

Contributed By DigiKey's North American Editors

2020-08-05

Editor’s Note: Analog-to-digital converters (ADCs) connect the analog to the digital world and so are a fundamental component of any electronic system that connects to the real world. They are also a key determining factor of a system’s performance. This series explores the fundamentals of ADCs, their various types, and their application. Part 1 of this series on analog basics discussed SAR ADCs. Part 2 discusses delta-sigma converters. Part 3 looks at pipeline ADCs. Here, Part 4 shows how delta-sigma ADCs can generate ultra-low-noise results. Part 5 explores difficult input driving issues for SAR ADCs.

The delta-sigma (ΔƩ) integrated circuit topology continues to appear in analog-to-digital converters (ADCs), rendering high resolution, high integration, and low-power solutions for process control, precision temperature measurement, and weighing scale applications.

The mystifying fact about this converter type is that it starts with a 1-bit conversion with a theoretical signal-to-noise ratio (SNR) of 7.78 decibels (dB), which is equivalent to 2 volts (VRMS) noise in a 5 volt system. From there, the ADC can blossom into a bona fide 24-bit delta-sigma converter providing a theoretical SNR of 146 dB, equivalent to 244 nanovolts (nV) rms noise in a 5 volt system.

This resolution leap from 1 bit to 24 bit relies upon oversampling algorithms, noise-shaping modulators, and digital filters to lower the quantization noise and increase the SNR. There is a way to avoid the complexity of the ΔƩ converter and its associated noise by instead using an amplifier input stage feeding into a 12- or 16-bit successive approximation register (SAR) ADC. This design path will work, but it requires more integrated circuits on the pc board and an increased BOM.

There is a better way to address the noise problem: tackle it head-on with an ultra-low-noise ΔƩ ADC.

This article briefly discusses the low-noise target application and how the ΔƩ ADC is designed internally to meet this requirement. It then introduces two ΔƩ ADCs from Texas Instruments—one emphasizing 24-bit precision, the other emphasizing 32-bit precision—while showing how to take advantage of the robust digital filtering in both.

Where the ΔƩ ADC fits

From an analog perspective, engineers need various degrees of accuracy when measuring the output of temperature, pressure, load cell, and optical sensors. Fundamentally, amplifiers enhance designers’ ability to quantify these small, and in most instances near DC, analog occurrences. The progressive digitization has brought about a change in perspective and capabilities, while enhancing the ability to store and modify the sensor signals.

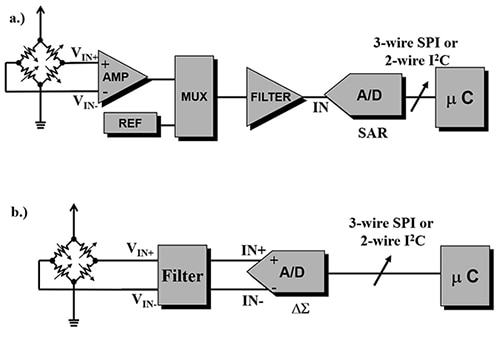

A typical sensor signal path toward digital capture starts with the sensor, moves through the gain, multiplexing, and filter stages, and then to the ADC (Figure 1a).

Figure 1: Two techniques to digitize a sensor signal use SAR ADCs (a) or ΔƩ ADCs (b). For high resolution circuits, the SAR ADC requires amplification and a fifth-order active filter, whereas the ΔƩ ADC requires a front-end, analog first-order passive filter. (Image source: A Baker’s Dozen: Real Analog Solutions for Digital Designers, B. Baker, ISBN 0-7506-7819-4)

Figure 1: Two techniques to digitize a sensor signal use SAR ADCs (a) or ΔƩ ADCs (b). For high resolution circuits, the SAR ADC requires amplification and a fifth-order active filter, whereas the ΔƩ ADC requires a front-end, analog first-order passive filter. (Image source: A Baker’s Dozen: Real Analog Solutions for Digital Designers, B. Baker, ISBN 0-7506-7819-4)

The converter in Figure 1a is a SAR ADC that can perform 12-bit to 18-bit conversions and can run at up to 10 megasamples per second (MSPS) conversion rates. The 16-bit converter provides 216 or 65,536 segments. In a 5 volt system, the least significant bit (LSB) is 5 volt/216298 or 76.3 microvolts (mV), with a theoretical SNR equaling 98 dB. It is possible to achieve higher granularity by exercising analog gain before the SAR converter.

The ΔƩ signal chain (Figure 1b) improves upon the resolution of the signal chain with a single converter, which also lowers the BOM. The ΔƩ ADC can provide 16-bit to 32-bit conversions. In this signal chain, the 24-bit ΔƩ ADC provides 224 or 16,777,216 segments. In a 5 volt system, the LSB is therefore 5 volts/224, or 298 nV, with a theoretical SNR equaling 146 dB. This resolution level brings the converter granularity closer to the sensor’s capabilities.

The 24-bit ΔƩ ADC is slower due to the internal digital filters that require time to implement filtering calculations. Typical output data rates for this converter range from a few hertz to 1 MSPS. Note that the analog filter is now an inexpensive first-order resistor-capacitor (RC) filter instead of the complex, three operational amplifier, fifth-order analog filter.

The differences between the noise of these two approaches is clear: the ΔƩ ADC’s low noise outperforms that of the SAR ADC (Table 1).

*Note: SNR = 6.02 N + 1.76, where N is the number of bits

|

Table 1: ADC segments, LSB, and theoretical SNR with full-scale input voltage of 5 volts for a 16-bit SAR ADC and 24-bit ΔƩ ADC. (Data source: Digi-Key Electronics)

The ΔƩ ADC offers an excellent solution for sensor solutions, such as temperature, pressure, and load cell, where the specification of speed is not critical; however, accuracy is paramount. This ADC can convert down to these small voltage values by using digital, instead of analog, noise reduction techniques.

Inside the ΔƩ ADC

The interior of the ΔƩ ADC is 80% digital. Typically, the converter receives the input signal and immediately changes that analog signal to digital. The converter then combines that digital signal with subsequent modulator conversions into a digital filter stage where the accumulated 1-bit signal is changed to multiple bits. The converter then serially sends the final multi-bit conversion to the awaiting microcontroller through the digital output stage.

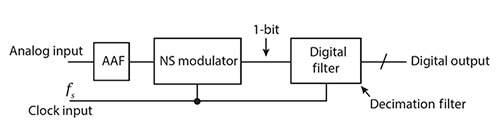

The analog signal first passes through an external first-order anti-aliasing filter (AAF). Then the noise-shaping (NS) modulator takes the analog signal and generates a 1-bit stream at the converter’s clock rate into the digital filter (Figure 2).

Figure 2: The typical ΔƩ puts the analog signal through a first-order AAF, generates a 1-bit stream using the NS modulator, then produces a multi-bit result at the digital output to a microcontroller. (Image source: CMOS: Mixed-Signal Circuit Design, 2nd Edition, J. Baker, ISBN 978-0-470-29026-2)

Figure 2: The typical ΔƩ puts the analog signal through a first-order AAF, generates a 1-bit stream using the NS modulator, then produces a multi-bit result at the digital output to a microcontroller. (Image source: CMOS: Mixed-Signal Circuit Design, 2nd Edition, J. Baker, ISBN 978-0-470-29026-2)

The digital filter clocks in multiple codes from the 1-bit stream and creates a full multi-bit result in the digital filter. These multi-bit results are serially transmitted through the digital output.

The ΔƩ modulator

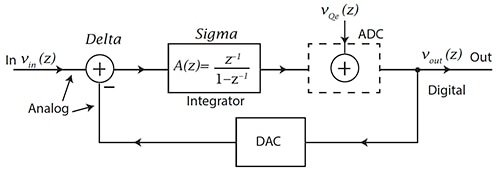

The number of integrator/feedback loops determine the order of the ΔƩ modulator. The first-order ΔƩ ADC modulator has a single integrator and feedback loop (Figure 3).

Figure 3: First-order modulator with an analog integrator and 1-bit ADC and a DAC in the feedback loop. VQe(z) is the quantization ADC noise. (Image source: CMOS: Mixed-Signal Circuit Design, 2nd Edition, J. Baker, ISBN 978-0-470-29026-2)

Figure 3: First-order modulator with an analog integrator and 1-bit ADC and a DAC in the feedback loop. VQe(z) is the quantization ADC noise. (Image source: CMOS: Mixed-Signal Circuit Design, 2nd Edition, J. Baker, ISBN 978-0-470-29026-2)

In Figure 3, the analog signal (VIN(z)) enters the Delta (Δ) portion of the modulator. The analog signal then goes through an integrator stage or Sigma (Ʃ) stage to a 1-bit ADC (with a sample rate of fS, per Figure 2), which can be a comparator. This now clocked digitized signal feeds back to the 1-bit digital-to-analog converter (DAC) and also proceeds to the VOUT(z) in the Δ stage. The 1-bit DAC presents an analog voltage to be subtracted from the analog input signal, VIN(z). The transfer function for this first-order modulator is:

![]() Equation 1

Equation 1

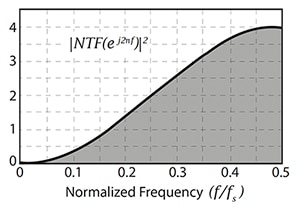

Because of the integrator and feedback loop, the modulator implements a noise-shaping algorithm on the modulator’s digital output data stream (Figure 4).

Figure 4: The noise-shaping function at the output of the ΔƩ modulator, where the noise transfer function (NTF) equals 1-z-1, where the 0.5 normalized frequency is equal to FS/2. (Image source: Understanding Delta-Sigma Data Converters, Schreier, Temes, ISBN 0-471-46585-2)

Figure 4: The noise-shaping function at the output of the ΔƩ modulator, where the noise transfer function (NTF) equals 1-z-1, where the 0.5 normalized frequency is equal to FS/2. (Image source: Understanding Delta-Sigma Data Converters, Schreier, Temes, ISBN 0-471-46585-2)

In Figure 4, the noise-shaping characteristic is the first step towards reducing conversion 1-bit quantization noise. With the noise pushed successfully into higher frequencies, a low pass digital filter completes the noise reduction process.

Higher-order modulators contain additional integrators and feedback loops. For instance, a third-order modulator has three integrators and three feedback loops. The noise-shaping function changes with modulator order by reducing noise near DC and increasing the shaped noise.

Higher-order modulators offer improved performance at the expense of more silicon hardware, reduced stability, and signal range.

The ΔƩ digital filters

The ΔƩ ADC operates by using oversampling (OS). Oversampling is the ratio of the sample rate of the modulator (FS) to the ADC output data rate (FD), per Equation 2:

![]() Equation 2

Equation 2

Oversampling improves ΔƩ ADC noise by digitally bandwidth limiting the noise-shaped data with a low-pass digital filter(s).

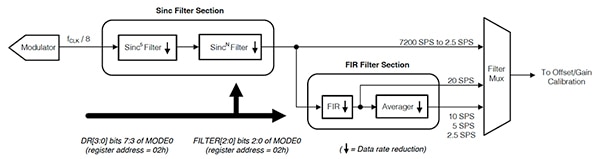

The two commonly used digital filters in the ΔƩ ADC are sin(pf)/pf (sinc) and linear-phase finite-impulse-response (FIR) filters. The digital filter implementation of the Texas InstrumentsADS1235, a 24-bit ΔƩ ADC, and the ADS1262 and ADS1263 32-bit ΔƩ ADCs (the ADS1263 integrates an auxiliary, 24-bit ΔƩ ADC intended for background measurements), offers a choice of the use of the sinc filters exclusively, or a combination of sinc followed by the FIR filters (Figure 5).

Figure 5: The ADS1235 24-bit ΔƩ ADC offers the use of the sinc filters exclusively, or a combination of sinc followed by the FIR filters. (Image source: Texas Instruments)

Figure 5: The ADS1235 24-bit ΔƩ ADC offers the use of the sinc filters exclusively, or a combination of sinc followed by the FIR filters. (Image source: Texas Instruments)

In Figure 5, the sinc (denoted “Sinc”) filter is a low-pass digital filter. The output (w(n)) of a sinc filter is calculated using Equation 3:

![]() Equation 3

Equation 3

The z-domain transfer function is:

Equation 4

Equation 4

The frequency response is:

![]() Equation 5

Equation 5

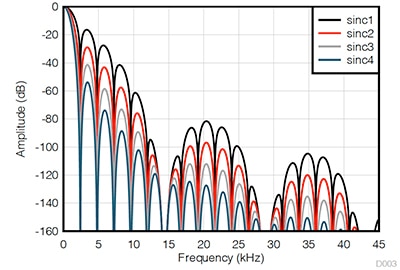

In Figure 5, SincN equates to N identical sinc filters in series. The graphical amplitude versus frequency response of the sinc filter has a comb-like appearance (Figure 6).

Figure 6: In the ADS1262/63, at 2400 samples per second (SPS) the numerous sinc digital filters—where sinc2 is equivalent to two identical SINC filters in series and sinc3 is equivalent to three identical sinc filters in series, etc.—create the comb-like frequency response. (Image source: Texas Instruments)

Figure 6: In the ADS1262/63, at 2400 samples per second (SPS) the numerous sinc digital filters—where sinc2 is equivalent to two identical SINC filters in series and sinc3 is equivalent to three identical sinc filters in series, etc.—create the comb-like frequency response. (Image source: Texas Instruments)

In Figure 6, the peaks and nulls are characteristic of the sinc filter response. The frequency response nulls occur at f (Hz) = N ·FD, where N = 1, 2, 3, .... At the null frequencies, the filter has zero gain.

Sinc filters (in series) create increased attenuation, causing increased latency. For instance, if a specific sinc filter calculation with an external clock rate of 7.3728 MHz produces an output data rate of 14400 SPS, the data rate of the output of the second sinc filter is 7200 SPS.

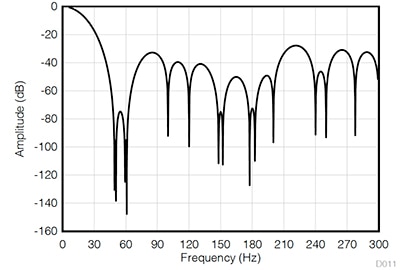

The low-pass FIR filter is a coefficient-based filter. The filter has simultaneous attenuation of 50 Hz and 60 Hz and harmonics at data rates of 2.5 SPS through 20 SPS. The conversion latency time of the FIR filter data rates is equivalent to a single cycle. The FIR filter receives pre-filtered data from the sinc filter and decimates the data to yield the output data rates of 10 SPS (Figure 7).

Figure 7: In the ADS1262/63, the FIR filter attenuates 50 Hz and 60 Hz signals to reduce line frequency interference and provides a series of response nulls placed close to these frequencies. The nulls repeat at the 50 Hz and 60 Hz harmonics. (Image source: Texas Instruments)

Figure 7: In the ADS1262/63, the FIR filter attenuates 50 Hz and 60 Hz signals to reduce line frequency interference and provides a series of response nulls placed close to these frequencies. The nulls repeat at the 50 Hz and 60 Hz harmonics. (Image source: Texas Instruments)

The FIR filter attenuates 50 Hz and 60 Hz signals to reduce line frequency interference and provides a series of response nulls placed close to these frequencies. The response nulls repeat at the 50 Hz and 60 Hz harmonics.

Precise low-noise ΔƩ ADC

An excellent example of a low-noise ΔƩ ADC is the previously mentioned Texas Instruments ADS1235 differential input 24-bit converter.

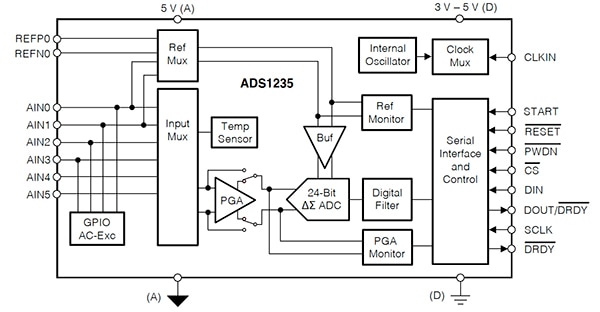

The ADS1235 is a precision, 7200 SPS, ΔƩ ADC with three differential or five single-ended inputs and an integrated programmable gain amplifier (PGA) with gains of 1, 64, and 128. This device also includes diagnostic features such as PGA over range and reference monitors. The ADC provides high-accuracy, zero-drift conversion data for high precision equipment, including weigh scales, strain gauges, and resistive pressure sensors (Figure 8).

Figure 8: The ADS1235 24-bit ΔƩ ADC block diagram with six-channel analog input and GPIO input multiplexer. (Image source: Texas Instruments)

Figure 8: The ADS1235 24-bit ΔƩ ADC block diagram with six-channel analog input and GPIO input multiplexer. (Image source: Texas Instruments)

For the ADS1235, the significant factors affecting noise performance are the data rate, PGA gain, and chop mode. Slower data rates bring in the digital filter’s corner frequency, hence reducing noise. Further, because of a two-point data averaging, performed in the chop mode, noise decreases by √2 compared to normal operation.

With a low frequency, 2.5 SPS data rate, and a 1 volt/volt PGA gain, the converter noise to the sinc3 digital output in a 5 volt system is 0.15 mVRMS (0.3 mV peak to peak (PP)) with an effective resolution of 24 bits, as well as a noise-free resolution of 24 bits. The theoretical, as well as actual, SNR of this device is 146 dB. As a matter of fact, with these conditions, the stable fourth-order modulator and the sinc1 through sinc4 filters produce 24 bits of effective resolution, as well as a noise-free resolution of 24 bits.

The ADS1235 has realized near-perfect 24-bit conversions for a 2.5 SPS data rate. The next generation ΔƩ ADC in this family is the Texas Instruments ADS1262/63. The primary difference between these devices is that the ADS1262/63 improves the low-noise circuitry and offers an extended 32-bit output data register.

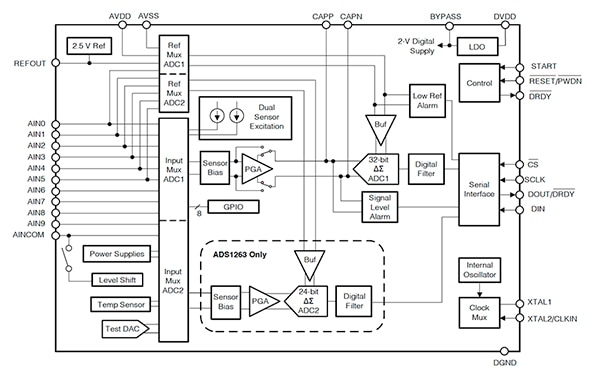

The ADS1262/63 has an improved low-noise CMOS PGA with gains of 1, 2, 4, 8, 16, and 32. The flexible analog front-end (AFE) incorporates two sensor-excitation current sources suitable for direct RTD measurements (Figure 9).

Figure 9: The ADS1262 and ADS1263 32-bit ΔƩ ADC block diagram with ten-channel analog input multiplexer. The ADS1263 has a second on-chip 24-bit ΔƩ ADC. (Image source: Texas Instruments)

Figure 9: The ADS1262 and ADS1263 32-bit ΔƩ ADC block diagram with ten-channel analog input multiplexer. The ADS1263 has a second on-chip 24-bit ΔƩ ADC. (Image source: Texas Instruments)

As with the ADS1235, the PGA gain, data rate, digital filter mode, and chop mode are the significant factors affecting noise performance with the ADS1262/63. With 32-bit resolution, the ADS1262/63 truly showcases the low-noise depth capability.

To start with, a stable fourth-order modulator and the sinc1 through sinc4 filters drive towards the production of 32 bits of effective resolution, as well as a noise-free resolution of 24 bits. By configuring a low frequency, 2.5 SPS data rate and PGA gain of 1 volt/volt (bypassed), the converter noise of the sinc3 digital output in a 5 volt system is 0.08 mVRMS (0.307 mVPP). This device surpasses the effective resolution with 26.9 bits, as well as a noise-free resolution of 25 bits. For this 32-bit system the theoretical SNR is 387 dB, with the actual SNR equaling 164 dB.

The differences between the noise of the 24-bit and 32-bit converters are clear, where the 32-bit ΔƩ ADC low-noise capability outperforms that of the 24-bit ΔƩ ADC (Table 2).

*Note: SNR = 6.02 N + 1.76, where N is # of bits

|

Table 2: Comparison of ADC rms noise, peak-to-peak noise, and SNR with full scale input voltage of 5 volts. (Data source: Digi-Key Electronics)

Conclusion

The ΔƩ ADC continues to push the low-noise limits with continually added capability. This article shows how this nearly digital, low-noise ADC maps directly into temperature, pressure, and load cell applications. A nuts and bolts discussion of a precision 24-bit ΔƩ ADC and 32-bit ΔƩ ADC outlines the path to realizing their ultra-precise characteristics.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.